Physical Address

304 North Cardinal St.

Dorchester Center, MA 02124

Physical Address

304 North Cardinal St.

Dorchester Center, MA 02124

Taalas transforma el sector al fijar modelos en silicio y multiplicar el rendimiento con costes mínimos.

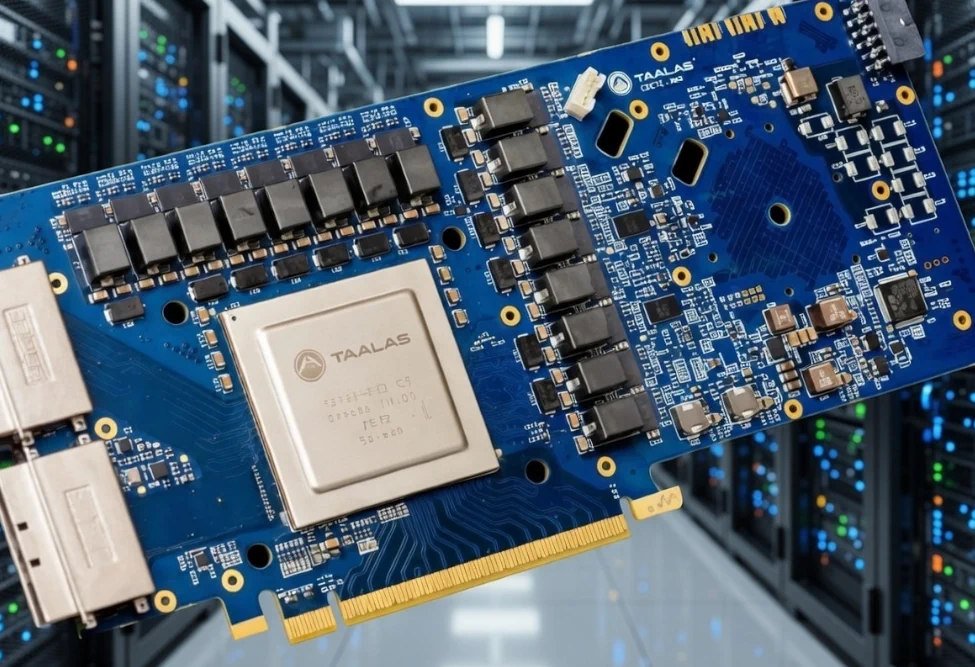

El avance de Taalas marca un punto de inflexión en el desarrollo de hardware para inteligencia artificial. La propuesta introduce un cambio profundo en la forma de ejecutar modelos lingüísticos. La idea consiste en fijar redes neuronales dentro del propio silicio. Esta técnica elimina capas de abstracción que frenan el rendimiento en sistemas actuales. La industria busca reducir latencias y aumentar el flujo de tokens por segundo. Aquí aparece Taalas con una solución que rompe esquemas y abre un camino distinto.

El mercado vive una presión creciente por la necesidad de respuestas inmediatas. La ejecución de modelos grandes exige memoria rápida, comunicación interna eficiente y un consumo energético razonable. Muchos fabricantes apuestan por integrar SRAM para acercar datos al procesador. Otros exploran arquitecturas masivas con miles de núcleos. Taalas decide abandonar la lógica de propósito general. La compañía diseña ASICs específicos para cada modelo. Esta estrategia permite optimizar cada ruta de cálculo y eliminar operaciones redundantes.

La plataforma convierte cualquier modelo en un diseño físico en solo dos meses. El proceso genera lo que llaman Hardcore Models. Estos modelos funcionan con una eficiencia muy superior a la de implementaciones tradicionales. La clave reside en dos pilares. El primero es la especialización extrema. Cada red neuronal se mapea directamente sobre el chip. El segundo es la fusión entre almacenamiento y computación. Esta unión reduce la distancia entre datos y unidades de cálculo. El resultado evita cuellos de botella típicos de arquitecturas convencionales.

El chip HC1 demuestra esta filosofía. Utiliza un nodo de 6 nm de TSMC y alcanza un tamaño cercano a 815 mm². Integra el modelo Llama 3.1 de ocho mil millones de parámetros. La densidad de cálculo se acerca al nivel de la memoria DRAM. Esta proximidad acelera la comunicación interna y reduce la latencia. La ausencia de sistemas complejos de refrigeración o empaquetado simplifica la fabricación. La ingeniería se concentra en el diseño del silicio y no en la infraestructura externa.

Los datos de rendimiento sorprenden. Taalas afirma que el HC1 ofrece diez veces más tokens por segundo que soluciones de gama alta. Además, reduce los costes de producción en un factor de veinte. Esta combinación altera la ecuación económica del sector. La velocidad deja de depender de grandes centros de datos. La eficiencia energética mejora de forma notable. La ejecución de modelos se vuelve más accesible para empresas que no pueden asumir infraestructuras gigantescas.

El enfoque presenta limitaciones. El HC1 aloja un modelo de ocho mil millones de parámetros. Los modelos punteros superan el billón de parámetros. Para escalar, Taalas recurre a configuraciones en clúster. La compañía asegura que ya ha probado un sistema de treinta chips con el modelo R1 de DeepSeek. La cifra alcanza doce mil tokens por segundo por usuario. Esta arquitectura distribuida permite aumentar capacidad sin rediseñar un chip descomunal. El reto ahora es la adopción comercial. El hardware queda ligado a un modelo concreto. No existe opción de modificar pesos o actualizar versiones sin fabricar un nuevo chip. Aun así, la velocidad obtenida compensa esta rigidez en muchos casos.

El sector observa este movimiento con interés. La tendencia hacia hardware especializado crece. La computación generalista muestra límites claros ante modelos cada vez más grandes. La propuesta de Taalas ofrece una vía alternativa. La reducción de costes y la mejora de rendimiento pueden acelerar la expansión de aplicaciones avanzadas. La industria seguirá de cerca la evolución de esta tecnología. El impacto puede ser profundo si la compañía mantiene su ritmo de desarrollo.

| Producto | Taalas HC1 |

| Tecnología | ASIC especializado para LLM |

| Modelo integrado | Llama 3.1 8B |

| Nodo de fabricación | TSMC 6 nm |

| Tamaño del chip | Hasta 815 mm² |

| Ventaja de rendimiento | 10x tokens por segundo frente a hardware actual |

| Coste de producción | 20x inferior a soluciones tradicionales |

| Arquitectura | Computación a densidad tipo DRAM |

| Escalabilidad | Clúster de 30 chips probado con DeepSeek R1 |