Physical Address

304 North Cardinal St.

Dorchester Center, MA 02124

Physical Address

304 North Cardinal St.

Dorchester Center, MA 02124

GTC 2026 prepara la presentación de Feynman, el mayor avance de NVIDIA en chips y aceleración de IA.

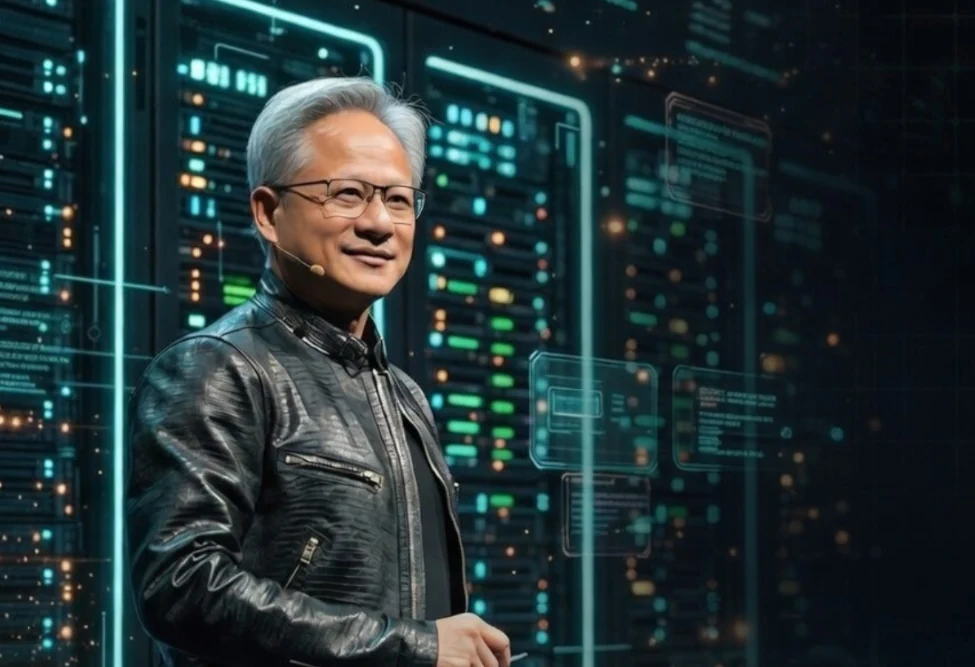

La edición GTC 2026 llega con expectativas enormes y una sensación clara de que la industria entra en una fase decisiva. Desde nuestro análisis, se aprecia que la conferencia quiere marcar un antes y un después en computación acelerada. El propio anuncio de la compañía indica que veremos tecnología nunca mostrada, y esa afirmación sitúa el foco en la arquitectura Feynman. El evento regresa a San José con un ambiente de anticipación que no se vivía desde la presentación de Blackwell. La palabra clave GTC 2026 ya domina las conversaciones del sector y refleja el interés por conocer el rumbo de la próxima década.

El informe publicado por el medio surcoreano Chosun Biz refuerza la idea de que Feynman será la protagonista. La información coincide con previsiones previas que apuntaban a un salto técnico sin precedentes. La arquitectura se apoyará en el nodo A16 de TSMC, una litografía de 1,6 nm que introduce el sistema Super Power Rail. Esta tecnología reorganiza la distribución energética dentro del chip para reducir pérdidas y mejorar la densidad. El nodo A16 representa el proceso más pequeño disponible en semiconductores y exige rediseños profundos en la estructura interna. Por ese motivo, se estima que NVIDIA será el único cliente durante la fase inicial de fabricación en volumen.

La adopción del nodo A16 no es el único elemento relevante. La posible integración de unidades LPU de Groq dentro del paquete Feynman añade una dimensión distinta. Las LPUs se diseñan para minimizar la latencia en inferencia, un parámetro crítico en modelos de gran tamaño. La idea de combinar GPU y LPU mediante un sistema de unión híbrida recuerda a la estrategia X3D vista en procesadores de AMD, donde se apilan capas para aumentar el rendimiento sin modificar la base del chip. La implementación en Feynman podría seguir un enfoque similar, aunque el desafío de producción sería mayor por la complejidad del empaquetado avanzado.

La latencia se ha convertido en un factor clave para cargas de trabajo de IA generativa, especialmente en contextos de respuesta inmediata. La integración de LPUs permitiría reducir tiempos de ejecución y mejorar la eficiencia en modelos de contexto largo. Esta tendencia se observa en estudios recientes sobre aceleradores especializados, que muestran mejoras significativas cuando se combinan arquitecturas heterogéneas. La presencia de Groq en este ecosistema marcaría un hito, ya que sería la primera vez que su tecnología aparece dentro de un producto de NVIDIA. La decisión encajaría con la estrategia de ampliar el rendimiento más allá del aumento de FLOPS, priorizando la experiencia final del usuario.

El paralelismo con la presentación de Vera Rubin resulta evidente. En aquella ocasión, la compañía mostró un recorrido completo por la arquitectura, sus capacidades y el calendario de producción. Feynman podría seguir el mismo patrón, con una explicación detallada del diseño, los módulos internos y los objetivos de rendimiento. La diferencia radica en la magnitud del salto técnico. El nodo A16, la posible integración de LPUs y la orientación hacia cargas de trabajo de IA extrema sitúan a Feynman como un punto de inflexión. La industria observa este movimiento con atención, ya que definirá la competencia en aceleración durante la próxima década.

Las previsiones actuales indican que la producción de Feynman comenzará en 2028. Ese calendario desplazaría los primeros envíos comerciales a 2029 o incluso 2030, según la estrategia de despliegue. La compañía suele mantener ciclos largos en sus arquitecturas de gama alta, por lo que este marco temporal encaja con su historial. GTC 2026 servirá como escaparate inicial para mostrar prototipos, especificaciones preliminares y demostraciones técnicas. El objetivo será establecer la narrativa de la próxima generación y preparar al mercado para un cambio profundo en computación acelerada.

El interés por GTC 2026 crece porque la industria necesita soluciones capaces de manejar modelos cada vez más grandes y complejos. La demanda de centros de datos, la presión energética y la necesidad de reducir latencias obligan a replantear la arquitectura de los chips. Feynman aparece como la respuesta a ese desafío. La combinación de un nodo extremo, un empaquetado avanzado y la posible integración de LPUs crea un ecosistema orientado a cargas de trabajo de nueva generación. La conferencia promete mostrar un adelanto de ese futuro y ofrecer una visión clara de cómo evolucionará la computación durante los próximos años.